Volume No. 13

Issue No. 2

May - August 2025

#### ENRICHED PUBLICATIONS PVT.LTD

JE - 18,Gupta Colony, Khirki Extn, Malviya Nagar, New Delhi - 110017. E- Mail: info@enrichedpublication.com

Phone :- +91-8877340707

#### **Aims and Scope**

Journal of Semiconductor Science & Technology is a journal of high quality devoted to the publication of original research papers on all aspects of semiconductor research and applications. The journal publishes original research papers on main aspects of experimental and theoretical studies of the properties of semiconductors and their interfaces. Appropriate subjects include but not limited to electrical properties, optical properties, device design, device fabrication, materials processing, materials and device analysis, process monitoring, reliability. Review articles in selected areas are published from time to time.

**Managing Editor**

Mr. Amit Prasad

**Editorial Assistant**

Ms. Shilpi Gandhi

(Volume No. 13, Issue No. 2, May - August 2025)

### **Contents**

| Sr. No | Article/ Authors                                                         | Pg No   |

|--------|--------------------------------------------------------------------------|---------|

| 01     | Analysis of Electrical Characteristics Changes Due to Physical Parameter | 1 - 15  |

|        | Variations in Dual-Gate Feedback Field Effect Transistor                 |         |

|        | -Hangwook Jeong 1 and Min-Woo Kwon2                                      |         |

| 02     | Analysis of the Switching Mechanism of Hafnium Oxide Layer with          | 16 - 24 |

|        | Nanoporous Structure by RF Sputtering                                    |         |

|        | -Jongho Lim1, Myung-Hyun Baek1, and Min-Woo Kwon,2                       |         |

| 03     | A Second-order Delta-sigma Modulator for Battery Management System       | 25 - 37 |

|        | DC Measurement                                                           |         |

|        | -Ji-Ho Park, Jun-Ho Boo, Jae-Geun Lim, Hyoung-Jung Kim, Jae-Hyuk         |         |

|        | Lee, Seong-Bo Park, Joo-Yeul Yang, and Gil-Cho Ahn                       |         |

| 04     | Design Optimization of L-Shaped Gate Negative Capacitance Si/Ge          | 38 - 54 |

|        | Heterojunction TFET With Channel Doping                                  |         |

|        | -Xinfeng Zheng, Weifeng Lü, Yubin Wang, Shuaiwei Zhao, and Honglei Huo   |         |

### Analysis of Electrical Characteristics Changes Due to Physical Parameter Variations in Dual-Gate Feedback Field Effect Transistor

#### Hangwook Jeong1 and Min-Woo Kwon2,

#### ABSTRACT

Conventional MOSFETs have reached a physical limit with a subthreshold swing of approximately 60 mV/dec at room temperature. To overcome this, various Beyond C-MOS devices are being researched, with thefeedback FET (FBFET) attracting attention due to its highly ideal subthreshold swing and high on-current. However, the FBFET operates much more sensitively compared to conventional MOSFETs. Therefore, analyzing theelectrical characteristics of the device as its physical parameters are varied is crucial in FBFET research. Despitethis importance, research and application of FBFETs have not yet made significant progress, and there is a lackof data analyzing the characteristic changes with parameter variations. In this study, we used a Dual-Gate FBFETto observe changes in electrical characteristics by varying the lengths of the gate and control gate, oxide and bodythickness, doping concentration, and the concentration and level of interface traps. An increase in the gate and Control gate lengths led to an increase in threshold voltage, and an increase in oxide thickness also resulted in a higherthreshold voltage. An increase in body thickness led to an increase in both on-current and threshold voltage, and anincrease in P- and N- doping concentrations resulted in a higher threshold voltage. Additionally, the application of interface traps in the gate and control gate regions increased the threshold voltage. This study's comparison andanalysis of these simulation results confirmed that parameter changes in the gate region critically impact deviceoperation more than changes in the control gate region. This finding highlights the need to pay closer attention to parameter variations in the gate region compared to the control gate during device design and manufacturing processes. We expect that this analysis will significantly aid further research and application of FBFET devices.

*Index terms:* Steep switching, low power, beyond C-MOS, sensitivity, control gate, dual-gate, feedback FET

#### I. INTRODUCTION

Conventional MOSFETs have reached the physical limit of a subthreshold swing (SS) of 60 mV/dec [1]. Thisphysical limit of the SS value poses a significant challengein reducing the operating voltage of devices, as it leads to a substantial increase in standby power due to leakage current [2]. As the demand for high switching speed and lowpower device operation grows, various beyond CMOS devices such as T-FET, NCFET, FEFET, and feedback field effect transistor (FBFET) are being actively researched[3]. Among these, FBFET stands out due to its extremelylow SS close to 0mV/decade and high on/off ratio, making it a promising candidate for low-power operation and steep switching behavior [4]. However, FBFETs operate more sensitively compared to conventional MOSFETs, especially the Dual-

Gate FBFET, which has more parameters and variables thanconventional MOSFETs. For instance, the Dual-GateFBFET has two gates and four different doping levels inthe body, making device analysis more complex. Additionally, the device operates with a very steep switching behavior due to its near 0mV/dec SS value, leading tohigh operational sensitivity. Therefore, a thorough analysis of the electrical characteristics resulting from changesin device parameters is crucial for the research and application of these devices. Despite this, fundamental analyses of Dual-Gate FBFET devices remain insufficient.

In this study, we analyze the impact of various parameters on the electrical characteristics of Dual-GateFBFET devices by altering each parameter and observing the resulting electrical behavior. We examine the effects of changing the gate and control gate lengths, oxideand body thicknesses, doping concentrations, and interface traps on the device's electrical characteristics. By assessing the influence of these parameter changes, we aimto identify which variations have the most critical impacton device operation. We expect that this research will significantly contribute to future studies and applications of highly sensitive Dual-Gate FBFET devices by providing a clear analysis of their electrical characteristics. In this paper, for convenience, we refer to Dual-Gate FBFET as FBFET.

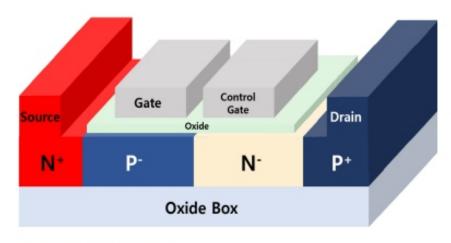

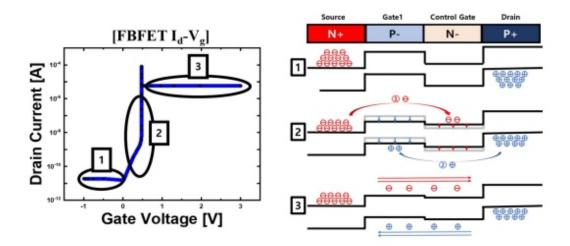

#### II. ARCHITECTURE AND MECHANISM

Fig. 1 illustrates a schematic model of the FBFET structure. Fundamentally, the device shares some similarities with conventional MOSFETs. The FBFET requires a silicon on insulator(SOI) structure to form a potential barrier and well. The silicon body is doped with N+, P-, N-, and P+ regions starting from the source area. The sourceand drain are in contact with the N+ and P+ regions, respectively, while the gate and control gate are positionedcentrally, side by side, on top of the oxide. Fig. 2 explains the operating principle of the FBFET using an energy band model. The following describes each

Fig. 1. FBFET structure.

Fig. 2. FBFET operation mechanism.

step of the energy band diagram in Fig. 2.

- (1) The P- region's energy band creates a potential barrier that blocks electrons from the N+ region, while the N- region forms a potential well that preventsholes from the P+ region from crossing.

- (2) When a positive voltage is applied to the gate, the potential barrier lowers, allowing electrons from the N+ region to enter the potential well. Theses electrons educe the well's depth, enabling holes from the P+region to move into the P− region. The presence of holes lowers the barrier, allowing more electrons tocross over. This process repeats and accelerates, creating positive feedback.

- (3) As the positive feedback continues, the potential barrier lowers, the well becomes shallower, and the energy band flattens. Once flattened enough, the device current flows rapidly.

Through this process, we can understand the basic operation of the FBFET. Additionally, at the preoperation stage, as shown in Fig. 2(1), the depth of the potential wellcan be adjusted by controlling the voltage of the controlgate. A deeper potential well delays the device's operation onset, indicating that the control gate voltage can be used to adjust the device's threshold voltage [5].

#### III. ANALYSIS METHOD

#### 1. Basic analysis information

The device analysis was conducted using SILVACO's T-CAD simulation. In this study, the trap analysis applied the interface trap model.

The device threshold voltage was measured using the Constant Current method. The FBFET has a SS close to 0mV, making it difficult to extract the differential value of the characteristic curve. Therefore, the Constant currentmethod is used instead of the Gm max technique. For the Constant current method, the reasonable turn-on current of the device is set to 10–6A. Given that the device exhibits an extremely small SS value and a steep turn-on characteristic, minor deviations at 10–6 A can be disregarded, making the application of the Constant current method appropriate.

#### 2. Parameter value

The analysis of the electrical characteristics in this study is based on observing the variation of drain currentwith gate voltage sweep. Here, a drain voltage of 0.8V and control gate voltage of 2V were applied to form the potential well, while the gate voltage was swept from 2V to 3V to observe the change in drain current.

Table 1 summarizes the design parameters of the deviceand doping concentrations used in the study. For comparison of the effects of gate and control gate lengths, the lengths of the gate and control gate were set to thesame 200nm. The oxide thickness was 10nm, and the bodythickness, which determines the height of the channel, was100nm. Regarding doping concentrations, P—doping wasprioritized and applied to the entire body, with the lowestdoping concentration at 1017cm—3. Subsequently, N—doping was applied at 1018cm—3, and finally, dopants were injected at a concentration of 1020cm—3 for N+ and P+. Eachparameter was chosen to optimize the observation of the device's electrical characteristics and is unrelated to thesuperior performance indicators of the device.

#### IV. RESULTS AND DISCUSSION

The electrical characteristics of the device were measured by varying the lengths of the gate and control gate, the thicknesses of the oxide and body, and the doping concentrations, along with variations in traps.

Table 1. (a) Design parameters, (b) Doping concentrations.

(a)

| Design para     | meters (nm) |

|-----------------|-------------|

| Gate length     | 200         |

| C.Gate* length  | 200         |

| Oxide thickness | 10          |

| Body thckness   | 100         |

| Full length     | 800         |

| Doping concentration (cm <sup>-3</sup> ) |                      |  |

|------------------------------------------|----------------------|--|

| N <sup>+</sup>                           | $1 \times 10^{20}$   |  |

| P-                                       | 1 × 10 <sup>17</sup> |  |

| $N^-$                                    | $1 \times 10^{18}$   |  |

| P <sup>+</sup>                           | $1 \times 10^{20}$   |  |

#### 1. Size variations

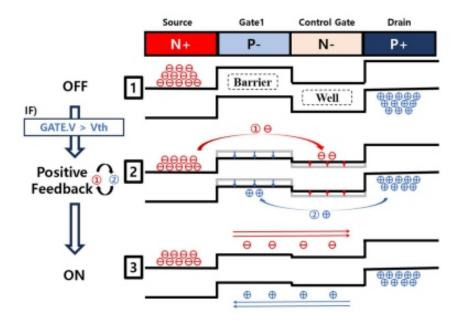

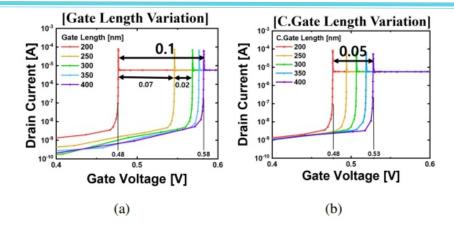

Fig. 3 presents a graph illustrating the electrical characteristics observed while varying the lengths of the gate and control gate. The lengths of the gate and control gate refer not only to the lengths of the contacted gate and control gate but also to the inclusion of the silicon body beneaththem. For example, doubling the gate length means that the silicon body beneath the gate is also doubled in size.

The lengths of the gate and control gate were varied from 200nm to 400nm at intervals of 50nm. It was observed that the threshold voltage increased with increasinglengths of both the gate and control gate. Furthermore, the variations in characteristics due to changes in gate lengthwere more pronounced compared to changes in the control gate.

Table 2 provides a summary of the changes in threshold voltage corresponding to variations in the lengths of the gate and control gate. The rate of change in threshold voltage due to variations in gate length was significantly higher compared to the rate of change in threshold voltagedue to variations in control gate length.

Additionally, when comparing the total change inthreshold voltage with reference points of 200nm and 400nm, the change in threshold voltage due to variations in gate length was 0.1 V, whereas for the control gate, itwas 0.05 V. It was evident that the change in thresholdvoltage due to variations in gate length was much greater. Upon examining the rate and magnitude of threshold volt-

**Fig. 3.** IV characteristics according to (a) Gate length variations and (b) Control gate length variations. An increase in gate and control gate length leads to a rise in threshold voltage.

**Table 2**. Threshold voltage differences with Gate and Control gate length variations. The effect of Gate length is more dominant than that of Control gate length.

| [V <sub>th</sub> differences in Gate and Control gate length variation] |                                                |         |  |  |

|-------------------------------------------------------------------------|------------------------------------------------|---------|--|--|

| Length variation[nm]                                                    | 200~250 _70% 250~300 _60% 300~350 _25% 350~400 | 200~400 |  |  |

| Gate V <sub>th</sub> difference [V]                                     | 0.07 0.02 0.008 0.006                          | 0.1     |  |  |

| C.GATE V <sub>st</sub> , difference [V]                                 | 0.017                                          | 0.05    |  |  |

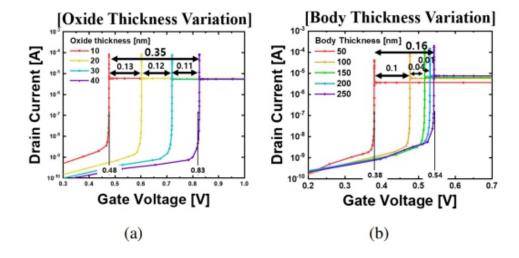

Fig. 4. IV characteristics according to (a) Oxide thickness variations and (b) Body thickness variations. An increase in oxide thickness raises the threshold voltage, while an increase in body thickness raises both the threshold voltage and the on-current.

## [V<sub>th</sub> differences in Oxide thickness variation]

| Thickness<br>Variation [nm]   | 10~20 | 20~30<br>7% —— -8.3 | 30~40 |

|-------------------------------|-------|---------------------|-------|

| V <sub>th</sub> difference[V] |       | 0.12                | 0.11  |

# [V<sub>th</sub> differences in Body thickness variation]

| Thickness<br>Variation [nm]                 | 50~100<br>-60%        | 100~150<br>%           |                       |

|---------------------------------------------|-----------------------|------------------------|-----------------------|

| V <sub>th</sub> difference [V]              | 0.1                   | <b>→</b> 0.04 <b>—</b> | → 0.01                |

| On current difference [log I <sub>d</sub> ] | 2.18×10 <sup>-6</sup> | 7.39×10 <sup>-7</sup>  | 8.86×10 <sup>-7</sup> |

age change, it was confirmed that variations in gate length had a greater impact on the electrical characteristics of the device compared to variations in control gate length.

Fig. 4(a) shows the variations in electrical characteristics of the FBFET with changes in oxide thickness. When the oxide thickness was varied from 10 nm to 40 nm atintervals of 10 nm, it was observed that the on-currentremained constant, while the threshold voltage increased with increasing thickness. This trend can be attributed to the FBFET having a structure similar to MOSFET, and the increase in oxide thickness leads to a decrease in the channel control ability of the gate.

Fig. 4(b) illustrates a graph showing the variations in electrical characteristics of the FBFET with changes inbody thickness. When the body thickness was varied from 50nm to 250 nm at intervals of 50nm, it was observed that the threshold voltage increased, and the on-current also increased.

Table 3 provides a summary of specific numerical values. The increase in threshold voltage with increasing body thickness can be understood as a result of the decrease in channel control ability due to the increase in channel height. Moreover, the increase in on-current withincreasing body thickness is attributed to the increase inchannel height, which leads to an increase in on-current.

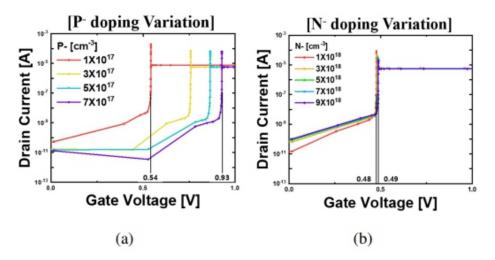

#### 2. Doping concentration variations

Dual-Gate FBFET operates with two gates, the gate and control gate. The doping concentrations of N+ and P+ at both ends are clear factors affecting the on-current levelafter the device turns on. Therefore, we varied only the doping concentrations of N- and P- that are considered meaningful for FBFET

doping analysis and examined the resulting graphs.

Fig. 5(a) shows the graph of the device's electrical characteristics when varying the doping concentration of P- in the body. It was observed that the on-current remainedconstant while the threshold voltage increased as the P-doping concentration varied from  $1\times117$  cm-3to  $7\times1017$ cm-3.

Fig. 5(b) shows the graph of the device's electrical characteristics when varying the doping concentration of N- in the body. When the N- body doping concentration varied from  $1\times1018$  cm-3to  $9\times1018$  cm-3, the on-currentremained constant, with a slight increase in the thresholdvoltage.

Table 4 summarizes the differences in threshold voltage due to doping concentration variations. Interestingly, despite the baseline concentration of N- being higher at1?1018cm-3compared to the baseline concentration of P- at 1?1017cm-3, the change in threshold voltage wassmaller when the N-concentration was varied by threefold, fivefold, and sevenfold. This observation suggests

**Table 4.** Threshold voltage differences with doping concentration variations. The effect of P<sup>-</sup> doping is more dominant than that of N<sup>-</sup> doping.

### [V<sub>th</sub> differences in Doping concentration variation]

| P- concentration<br>Variation [cm <sup>-3</sup> ] | 1×10 <sup>17</sup><br>~3×10 <sup>17</sup> | 3×10 <sup>17</sup><br>~5×10 <sup>17</sup> | 5×10 <sup>17</sup> ~7×10 <sup>17</sup>    |

|---------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| V <sub>th</sub> difference [V]                    | 0.22                                      | 0.11                                      | 0.06                                      |

|                                                   |                                           |                                           |                                           |

| N- concentration<br>Variation [cm <sup>-3</sup> ] | 1×10 <sup>18</sup><br>~3×10 <sup>18</sup> | 3×10 <sup>18</sup><br>~5×10 <sup>18</sup> | 5×10 <sup>18</sup><br>~7×10 <sup>18</sup> |

that changes in P- doping in the body have a more significant impact on the device compared to N-doping.

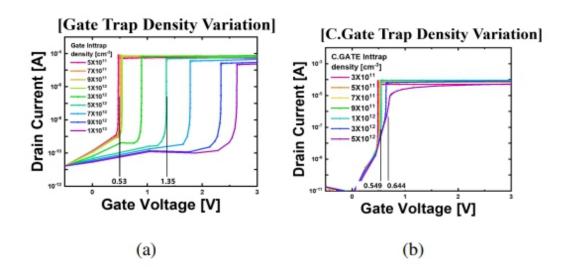

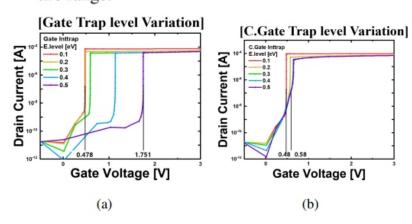

#### 3. Interface trap variations

Interface traps in FBFET occur at the boundary between the silicon body and the oxide layer. We classified the application of interface traps into those applied to the gate control gate separately, as well as those applied to theentire range, and aimed to assess the influence of trap density and trap level variations on interface traps.

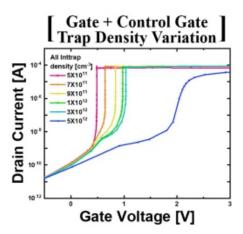

Fig. 6 depicts the graph of electrical characteristic variations when interface traps are applied below the gate or control gate ranges, with trap density varied. In this case, the trap level is kept constant at 0.56 eV. It is observed that regardless of the position of the gate or control gate, an increase in interface trap density leads to an increase inthreshold voltage.

Table 5 summarizes the changes in threshold voltagewithin the range of trap densities from  $9 \times 1011$  cm-3 to  $5 \times 1012$  cm-3, as shown in Fig. 6. It is notable that the change in threshold voltage due to the application of gateinterface traps is significantly larger compared to that of the control gate. Additionally, Fig. 7 presents the results of

Fig. 6. IV characteristics according to Trap density variations. An increase in both Gate trap and Control gate trap density leads to increase in threshold voltage.

**Table 5.** Threshold voltage differences with Trap density variations. The effect of Gate trap is more dominant than that of Control gate trap.

[V<sub>th</sub> differences in trap density variation]

| Gate trap<br>Variation [cm <sup>-3</sup> ]   | 9×10 <sup>11</sup><br>~1×10 <sup>12</sup> | 1×10 <sup>12</sup><br>~3×10 <sup>12</sup> | 3×10 <sup>12</sup><br>~5×10 <sup>12</sup> |

|----------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| V <sub>th</sub> difference [V]               | 0.014                                     | 0.35                                      | 0.46                                      |

| 6.6-4-4                                      |                                           | 4 4012                                    | 2 4212                                    |

| C.Gate trap<br>Variation [cm <sup>-3</sup> ] | 9×10 <sup>11</sup><br>~1×10 <sup>12</sup> | 1×10 <sup>12</sup><br>~3×10 <sup>12</sup> | 3×10 <sup>12</sup><br>~5×10 <sup>12</sup> |

Fig. 7. IV characteristics according to Trap density across the entire range.

**Fig. 8.** IV characteristics according to Trap level variations. An increase in both Gate trap and Control gate trap level leads to increase in threshold voltage.

observing electrical characteristic variations with interface trap density changes applied to the entire range.

Fig. 8 illustrates the graph of electrical characteristic variations when interface traps are applied below the gateor control gate ranges, with trap level varied. Both graphs show that threshold voltage increases with an increase intrap level.

Table 6 summarizes the changes in threshold voltage with variations in trap level, as depicted in Fig. 8. It is notable that the changes in threshold voltage due to variations in gate trap level are significantly larger compared to those resulting from variations in control gate trap level. Additionally, Fig. 9 presents the graph of observing elec-

**Table 6.** Threshold voltage differences with Trap level variations. The effect of Gate trap is more dominant that that of Control gate trap.

[V<sub>th</sub> differences in trap level variation]

| Gate trap                      | 0.1   | 0.2   | 0.3   | 0.4   |

|--------------------------------|-------|-------|-------|-------|

| Variation [eV]                 | ~0.2  | ~0.3  | ~0.4  | ~0.5  |

| V <sub>th</sub> difference [V] | 0.011 | 0.105 | 0.547 | 0.609 |

|                                |       |       |       |       |

| C.Gate trap                    | 0.1   | 0.2   | 0.3   | 0.4   |

| Variation [eV]                 | ~0.2  | ~0.3  | ~0.4  | ~0.5  |

trical characteristic variations with changes in trap level applied to the entire range.

#### 4. Discussion

The increase in the lengths of the gate and control gate leads to an increase in channel length, resulting in an increase in threshold voltage. As the gate length increases, itdelays the accumulation of electrons in the potential wellbecause the longer channel slows down the electron transport. This is similar to the decrease in current observed in conventional MOSFETs when the channel length increases [6]. In contrast, an increase in control gate lengthleads to an extension of the potential well, requiring morecharge to raise the energy band sufficiently. Therefore, increases in both the gate and control gate lengths delay the FBFET's operation time.

An increase in oxide thickness reduces the gate's control over the channel, leading to an increase in the threshold voltage [7]. This reduced control means a higher gatevoltage is required to lower the potential barrier sufficiently, resulting in an overall increase in threshold voltage.

An increase in body thickness leads to an increase in the on-current. Since FBFETs must maintain electrons and holes in the feedback mechanism, they are fabricated on

Fig. 10. IV characteristic of FBFET and energy band.

SOI wafers. Once the FBFET turns on, the entire body acts as the channel. Thus, a thicker body increases the channel height, enhancing the on-current.

An increase in doping concentration leads to an increase in threshold voltage. Specifically, an increase in P- doping concentration raises the potential barrier, thereby increasing the threshold voltage. Similarly, an increase inN- doping concentration increases the depth of the potential well, also resulting in a higher threshold voltage.

An increase in the concentration of interface traps also raises the threshold voltage. On the gate side, as the density and energy level of the interface traps increase, more electrons from the source are trapped during the feedbackmechanism, decreasing the interface potential and raising the energy band [8,9]. As

a result, more voltage must be applied to the gate to turn the device on. Additionally, mobility decreases due to the interface traps, causing both anincrease in threshold voltage and a reduction in oncurrent[10]. On the control gate side, increased interface trap density and level cause holes from the drain to be trapped during the feedback mechanism, raising the interface potential and lowering the energy band. This deepens the potential well, requiring more time to turn the device on. Therefore, the threshold voltage increases and the on-current decreases due to the interface traps.

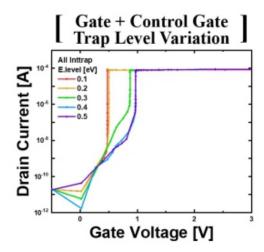

In the variations of length, doping concentration, and trap density, it was observed that changes in parameters in the gate region led to larger variations compared to changes in parameters in the control gate region. This phenomenon can be understood through the operational process of the FBFET.Fig. 10 shows the Id-Vg graph of the FBFET alongsidethe energy bands representing the operational principles of the FBFET.

The operational points are categorized intothree regions. Let's closely examine region 2 (the point atwhich the device turns on). Changes in the parameters of the control gate alter the depth and length of the potential well, thus influencing the operational point of the device. However, it's essential to remember that the filling of freeelectrons in the potential well and the occurrence of positive feedback fundamentally result from the prior lowering of the potential barrier in the gate region. Ultimately, the device's operational point heavily depends on potential barrier in the gate region. Through this, it becomes evident how changes in gate parameters have a more pronounced effect on the operational point of the device compared to changes in control gate parameters.

#### V. CONCLUSIONS

Various steep switching devices have been researched, and among them, we examined the electrical characteristic changes of the FBFET with variations in device parameters. Through this study, we found that changes in gate parameters have a more significant impact on the thresholdvoltage characteristics of the device compared to changes in control gate parameters.

The FBFET is highly sensitive, requiring thorough analysis for both research and practical applications. This study holds significant value due to the lack of detailed analysis on the electrical characteristics of dual-gate FBFETs with varying parameters. Additionally, the FBFET has a significant drawbackin its large hysteresis characteristics [11]. The inherent mechanism of the FBFET leads to a critical issue wherethe device does not easily turn off even under reverse biasafter turning on. So, adjusting the drain voltage is required to turn off the device in a logic circuit. Despite this disadvantage, the device has significant potential because it consumes far less energy compared to conventional MOSFETs, due to its SS being close to 0 [12]. Additionally, its ability to adjust operation time by controlling the control gate

voltage is a strong advantage, making it a promising candidate for use in logic operation systems [13].

The advantages of the FBFET are clear. It exhibits avery steep switching characteristic with an SS close to 0 mV/dec, enabling high-speed and low-power operation. Therefore, it is crucial to conduct focused additional analysis and follow-up research to mitigate the disadvantages of the device while maximizing its advantages.

#### **ACKNOWLEDGMENTS**

This study was supported by the Research Program funded by the SeoulTech(Seoul National University of Science and Technology).

#### REFERENCES

- [1] Kin P. Cheung, "On the 60 mV/dec @300 K limit for MOSFET subthreshold swing," Proc. of 2010 International Symposium on VLSI Technology, System and Application, Hsinchu, Taiwan, pp. 72-73, 2010..

- [2] K. Im, M. Kim, Y. Kim, D. Lim, and S. Kim, "Researchon silicon nanowire transistors for future wearable electronic systems," Vacuum Mgazine, Korea Science, pp. 15-18, 2016.

- [3] J. Chowdhury, A. Sarkar, K. Mahapatra, and J. K. Das, "More-than-moore steep slope devices for higher frequency switching applications: A designer's perspective," Physica Scripta, IOP, 2024.

- [4] C. Lee, J. Sung, and C. Shin, "Understanding of feedbackfield-effect transistor and its applications," Appl. vol. 10, 3070, 2020.

- [5] J. Lee, M. Cha, and M. -W. Kwon, "Charge trap flash structure with feedback field effect transistor for processing inmemory," Journal of Semiconductor Technology and Science, IEIE, vol. 23, no. 5 pp. 295-302, 2023.

- [6] H. Liu, A. T. Neal and P. D. Ye, "Channel length scalingof MoS2 MOSFETs," ACS NANO, ACS Publication, vol.6, no. 10, 2012.

- [7] S. K. Sinha and S. Chaudhury, "Impact of oxide thickness on gate capacitance A comprehensive analysis on MOSFET, Nanowire FET, AND CNTFET," IEEE Transactions on Nanotechnology, IEEE, vol. 12, no. 6, pp. 958-964, 2013.

- [8] B.-J. Park, H.-S. Kim, and S.-H. Hahm, "Interface trap effects on the output characteristics of GaN Schottky barrier," Journal of Sensor Science And Technology, KSS, vol. 31, no. 4, pp, 271-277, 2022.

- [9] Y. Yang, Y.-S. Park, J. Son, K. Cho, and S. Kim, "Simulation studies on electrical characteristics of

silicon nanowire feedback field-effect transistors with interface trap charges," Scientific Reports, Nature, 2021.

[10] H. Jafari, S. A. H. Feghhi, and S. Boorboor, "The effect of interface trapped charge on threshold voltage shift estimation for gamma irradiated MOS device," Radiation Measurements, Elservier, vol. 63, pp. 69-77, 2014.

[11] S. S. Katta, T. Kumari, S. Das, and P. K. Tiwari, "Design and performance assessment of a vertical feedback FET," Microelectronics Journal, Elsevier, vol. 137, 2023.

[12] M.-W. Kwon, M.-H. Baek, S. Hwang, K. Park, T. Jang, T. kim, J. Lee, S. Cho, and B.-G. Park, "Integrate-and-fireneuron circuit using positive feedback field effect transistor for low power operation," Journal of Applied Physics, AIPPublishing, vol. 124, no. 15, 2018.

[13] J. Lee and M.-W. Kwon, "Positive feedback field effect transistor based on vertical NAND flash structure for immemory computing," JJAP, The Japan Society of AppliedPhysics, vol. 63, 2024.

Hangwook Jeong is currently pursuing a bachelor's degree from the Department of Electronic Enginee- ring at Gangneung Wonju National University (GWNU). He is con-ducting research on the analysis of next generation semiconductor FBFET device characteristics and the study of In memory computing using FBFETs at the Intelligent Semiconductor Device & Circuit Design Laboratory (ISDL).

Min-Woo Kwon received his B.S. and Ph.D. degrees in electrical and computer engineering from Seoul National University (SNU) in 2012 and 2019, respectively. From 2019 to 2021, he worked at Sam sung Semiconductor Laboratories, where he contributed to the development of 1x nm DRAM cell. From 2021 to 2024, he worked at Gangneung-Wonju National University (GWNU) as an assistant professor in the Department of Electric Engineering.

Since 2024, he has been conducting research in the Department of Electronic Engineering at Seoul National University of Science and Technology, where he is currently a professor

# **Analysis of the Switching Mechanism of Hafnium Oxide Layer with Nanoporous Structure by RF Sputtering**

#### Jongho Lim1, Myung-Hyun, and Min-Woo Kwon,2

#### ABSTRACT

As the demand for advanced memory technologies grows, the development of next-generation mem ory devices is required. One promising candidate is resistive random access memory (RRAM), which is advantageous for high-density integration in three-dimensional vertical crossbar array architectures due to its simple metal-insulator-metal structure [1]. In this study, we fabricated an RRAM device and analyzed the of the HfOx insulating layer when it possesses a nanoporous structure. The HfOx insulating layer was deposited to induce the nanoporous structure by RF sputtering. When the HfOx insulating layer has a nanoporous structure, the device exhibits a minimum current existing at a specific voltage and rectifying properties. These characteristics result from the migration of oxygen vacancies and the presence of oxygen ions in the pores. Depending on the applied voltage magnitude, the internal electric field created by the negatively charged oxygen ions in the pores shifts the voltage point of the minimum current. In addition, the Schottky-like barrier modulation induced by migration of oxygen vacancies leads to a non-linear I-V switching behavior. The resistive switching mechanism observed in the nanoporous insulating layer plays a crucial role in enhancing the device's performance. These findings provide valuable insights into understanding the electrical characteristics of other RRAM devices with similar structures.

Index terms: RRAM, HfOx, rectifying properties, nanoporous structure, Schottky-like barrier modulation

#### I. INTRODUCTION

Metal-oxide-based RRAM is one of the most promising non-volatile memory devices due to its high-speed switching, next-generation non-volatile memory technologies, low power consumption, high scalability, and compatibility with complementary metal-oxide semiconductor(CMOS) technology [2,3]. The resistive switching mechanism is typically attributed to the formation and rupture ofconductive filaments within the dielectric layer, which canbe induced by applying an external voltage. This mechanism makes RRAM a promising candidate for future memory applications. Among high-k materials, hafnium oxide (HfOx) is one of the most widely used dielectric materials for the development of high-performanceRRAM devices [4]. Hafnium-based high-k dielectrics offer high dielectric constants, excellent thermal stability, and compatibility with existing semiconductor fabricationprocesses [5]. In addition, HfOx exhibits a high affinity foroxygen, which significantly facilitates the formation andmigration of oxygen vacancies (Vo), an essential aspect of the resistive

witching mechanism. These properties make HfOx a highly desirable material for enhancing the relia bility and performance of RRAM devices. Consequently, we have selected hafnium oxide as the switching layer forour RRAM device. The structure of the RRAM device is a metal-insulator-metal (MIM) structure with an insulating layer sandwiched between two metal electrodes. Manystudies have explored high-density memory structures using the simple MIM configuration of RRAM. In this cross bar array structure, the sneak path current that occurs between the memory cells will induce read-out errors in the array [6]. Therefore, the sneak path current that occurs between the cells must be suppressed. To solve the sneakpath problem, several research groups have used transistors or diodes in each memory cell [7]. However, the use of selector device in memory cells leads to some limitations. First, the selector device must match the operating range with the memory device [8]. Second, the addition of a selector device results in an increase in cell size, which is a limiting factor for the integration density of memristor systems. Therefore, the self-rectifying resistive switching memory becomes one of the most promising solutions to overcome the sneak path current problem without re quiring an additional diode. We have derived these selfrectifying characteristics to a phenomenon that emerges by RF sputtering the switching layer. Due to the nature of the sputtering process, oxide films deposited by sputtering generally have nanoporous structures, and the existence of these pores affects the performance of the device[9-11]. In this work, we have fabricated a RRAM device inwhich the HfOx layer is sandwiched between titanium (Ti)and molybdenum disulfide (MoS2) layers and studied the effect of the nanoporous structure on resistive switchingbehavior. The resistive switching characteristics of the device have induced by RF sputtering HfOx insulating layerto form pores. The device shows self-rectifying resistives witching behavior with a nonlinear switching characteristics. This study will provide valuable insight into the electrical characteristics of other similar devices.

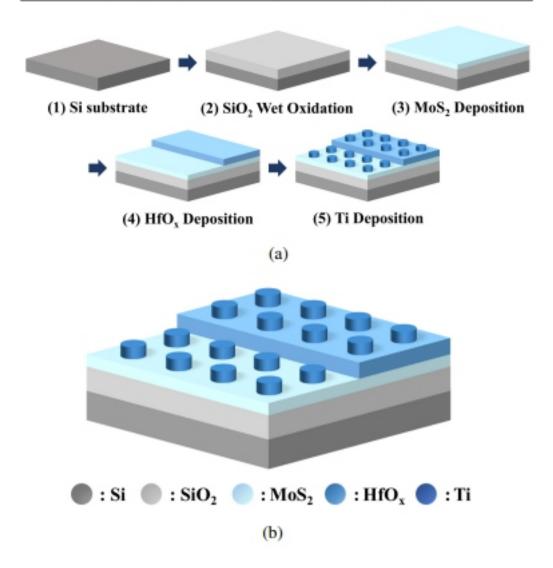

#### II. DEVICE FABRICATION

The fabrication process of the Ti/HfOx/MoS2 RRAM device is depicted in Fig. 1(a). The Ti/HfOx/MoS2 RRAMdevice was fabricated on a square SiO2/Si wafer substrate. Fig. 1(b) shows the schematic of the RRAM device structure. The fabrication process of the Ti/HfOx/MoS2 RRAMdevice is described in the following. First, the SiO2/Sisubstrate was rinsed with acetone, isopropyl alcohol, anddeionized water for 5 minutes for device fabrication andthen dried with N2 gas. Then, both the electrode and theswitching layer were deposited by RF sputtering. The detailed conditions of the sputtering method that used forthe fabrication of the RRAM device are summarized inTable 1. All the RF sputtering processes were carried outunder the same conditions. The MoS2 switching layer asthe bottom electrode was deposited on SiO2/Si substrate for 10 minutes. After that, to study the resistive

switching characteristics of the nanoporous structure, HfOx film was

Table 1. RF sputtering deposition conditions.

| RF power            | 100 W            |

|---------------------|------------------|

| Deposition pressure | 45 mTorr         |

| Temperature         | Room temperature |

| Ar gas flow         | 50 seem          |

Fig. 1. (a) The fabrication process of nanoporous HfO<sub>x</sub> based on RRAM device; (b) The proposed Ti/HfO<sub>x</sub>/MoS<sub>2</sub> RRAM structure.

deposited as an insulator using a shadow mask for 20 minutes. Finally, Ti top electrode with a diameter of 400 µm was deposited through a shadow mask.

#### III. RESULTS AND DISCUSSION

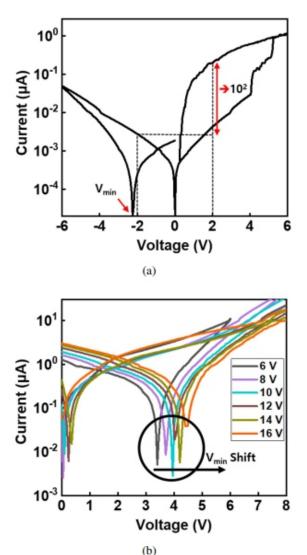

The resistive switching characteristics of the Ti/HfOx/ MoS2 RRAM device were measured by a vacuum probestation and semiconductor parameter analyzer (AgilentB1500). The voltage bias was applied to the top electrode, while the bottom electrode was grounded. Fig. 2(a)shows the I-V characteristics of the two-terminal electrodenanoporous HfOx memory device. A positive voltagesweep was followed by a negative voltage sweep. The I-V curve exhibits two main characteristics. The first characteristic is self-rectifying resistive switching behavior. During forward and reverse voltage sweep, the Ti/HfOx/MoS2RRAM device exhibited a rectifying current ratio of ap proximately 102at ±2 V. This self-rectifying property can be explained by barrier modulation due to the migration

Fig. 2. (a) Representative I-V characteristics of the HfOx device; (b) Position of Vmin when supply voltage is 6 V to 16 V; (c) I-V curve for −5 V to 5 V and 5 V to −5 V voltage changes.

of Vo within the nanoporous HfOx layer [12]. The selfrectifying switching operation of the device, which exhibits minimal current flow at reverse voltage compared to positive voltage, can address the problem of sneak path current, one of the major issues in crossbar arrays [13]. The second characteristic is that the voltage point of theminimum current during the reverse sweep does not return to 0 V but exists at a specific negative voltage. In thenanoporous switching layer, an internal electric field maybe formed in accordance with an external electric field inthe pores [12]. Such a characteristic enables a wide rangeof switching operations. We conducted two experiments demonstrate these two features (rectification characteristics and the specific voltage points of the minimum current) [14]. First, we set the applied voltage between 6 Vand 16 V to observe the relationship with Vmin (voltageposition of minimum current). Fig. 2(b) shows the changeof Vmin according to the applied voltage. As the appliedvoltage increased, a linear relationship emerged, with Vminshifting in the positive direction. This linear relationshipsupports the idea that the internal electric field created by the negatively charged oxygen ions in the pores influences the external electric field [14]. The external electric field provides

provides the necessary energy for the migration of oxygen ions within the insulating layer, causing them to move and become trapped in the defects or pores. Trapped oxygenions can lead to the formation of a local internal electricfield within the insulating layer. It indicates that more negatively charged oxygen ions in the pores of the switchinglayer can move as the applied voltage increases. The operation of the nanoporous RRAM device shows that the formation of the internal electric field affects the resistancestates of the device, allowing for the presence of a minimum current at a specific voltage. The results of the first experiment show that during the voltage sweep, the external electric field is offset by the internal electric fieldgenerated by the nanoporous HfOx layer, counterbalancing at a specific voltage point, so that the minimum current does not return to 0 V but exists at a specific voltagepoint. In the second experiment, the rectification characteristics resulting from Schottky barrier modulation due to the migration of Vo within the insulating layer were investigated. The impact of voltage polarity on current andbarrier modulation is explained by the I-V characteristics of the device, as illustrated by two different sweeps. Eachinitial voltage polarity was applied in both positive andnegative directions, and the current flow was observed in the subsequent sweeps. Fig. 2© shows the blue curve representing the voltage sweep from 5 V to -5 V, while thered curve corresponds to the sweep from -5 V to 5 V. As shown in the I-V characteristics, the current response

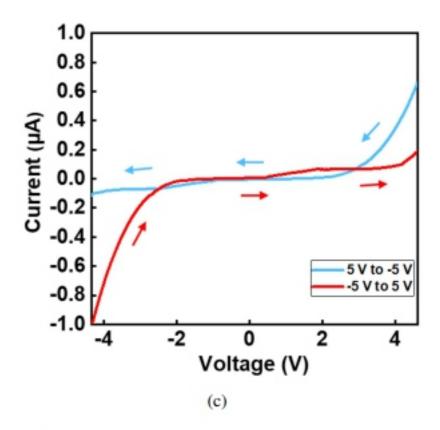

Fig. 3. Schematic cross-section of the Ti/HfO<sub>x</sub>/MoS<sub>2</sub> device structure with the negative oxygen ions in the pores driven by the external electric field.

depends on the direction of the initial voltage sweep. In the 5 V to -5 V sweep (blue curve), higher current isobserved in the positive voltage region compared to thenegative voltage region. Conversely, in the -5 V to 5 Vsweep (red curve), higher current is observed in the negative voltage region. This non-linear I-V characteristic canbe attributed to the migration of Vo within the nanoporous insulating layer, modulating the Schottky barrier at themetal-insulator interface; this corresponds to the schematics of Fig. 3 [14]. When voltage is applied, Vo within the nanoporous insulating layer begin to move according to the polarity of the electric field. In the positive sweep (5V to -5 V), Vo are pushed towards the bottom electrodeby the initially applied positive voltage at the top electrode. The accumulation of

of Vo at one end reduces the energy barrier, forming an Ohmic-like contact and enhancing current flow in the positive voltage region. Conversely, at the opposite interface, the relative lack of Vo form aSchottky-like contact, suppressing current flow during the subsequent negative voltage sweep (0 V to -5 V). In thereverse sweep (-5 V to 5 V), due to the polarity of theapplied voltage, Vo initially move towards the top electrode. Such movement increases the barrier height at theinterface between the bottom electrode and the insulating layer, forming a Schottky-like barrier, while an Ohmiclike contact is established at the opposite interface. Similarly, the barrier modulation set by the initial negative voltage suppresses current flow during the subsequent positive voltage sweep (0 V to 5 V). The results of the second experiment demonstrate that the migration of Vo, influencedby voltage polarity, results in the formation of Ohmic-likeand Schottky-like contacts at the two interfaces of the insulating layer. The barrier modulation exhibits Schottkydiode behavior, showing non-linear I-V switching operation as the device's self-rectifying characteristic. Overall, his analysis explains the critical role of Vo migration and internal electric field generation within the nanoporousHfOx insulating layer. The linear relationship between applied voltage and the voltage point of minimum currenthighlights the dynamic nature of the internal electric field, driven by negatively charged oxygen ions. Additionally, the observed Schottky-like and Ohmic-like contacts, dependent on voltage polarity, underline the potential of this RRAM device in mitigating sneak path currents in highdensity crossbar arrays. These insights will not only advance our understanding of the switching mechanisms innanoporous HfOx-based RRAM but also pave the wayfor the optimization and development of next-generation memory technologies.

#### IV. CONCLUSION

In summary, we analyzed the characteristics that emerge when the switching layer has a nanoporous structure. The device can be fabricated at room temperature and exhibits two distinct features that set it apart from conventional memory devices. Firstly, the position of Vmin varies with the applied voltage, which was demonstrated to bedue to the internal electric field created by the migration of negatively charged oxygen ions within the pores. The linear relationship observed between the applied voltage and Vmin indicates a broad range of switching characteristics that can be achieved across a range of operating voltages. Secondly, the self-rectifying resistive switching behavioris shown to be due to Schottky-like barrier modulation influenced by the initial polarity of the applied voltage. This self-rectifying property has the potential to suppress sneak path currents from unselected cells in 3D vertical crossbar array structures. This analysis demonstrates that nanoporous hafnium-based memory devices offer significant advantages compared to non-porous oxide-based memory devices. The results of this study not only enhance the understanding of the switching mechanisms of these devices but also pave the way for the development of more efficient and reliable memory technologies.

#### **ACKNOWLEDGMENTS**

This research was supported by Semiconductor R&D Support Project through the Gangwon Technopark(GWTP) funded by Gangwon Province(No.GWTP 2024-029) and this work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MIST)(2009-0082580.

#### **REFERENCES**

- [1] H. LI, et al., "Memristive crossbar arrays for storage and computing applications," Advanced Intelligent Systems, vol. 3 no. 9, 2100017, 2021.

- [2] D. Kumar, et al., "Metal oxide resistive switching memory: Materials, properties and switching mechanisms," Ceramics International, vol. 43, pp. S547-S556, 2017.

- [3] H. S. Wong, H.-S. Philip, et al., "Metal-oxide RRAM," Proceedings of the IEEE, vol. 100, no. 6, pp. 1951-1970,2012.

- [4] H.-Y. Lee, et al., "Low-power switching of nonvolatile resistive memory using hafnium oxide," Japanese Journal of Applied Physics, vol. 46, no. 4S, 2175, 2007.

- [5] M. Y. Chan, et al., "Resistive switching effects of HfO2high-k dielectric," Microelectronic Engineering, vol. 85,no. 12, pp. 2420-2424, 2008.

- [6] H.-Y. Chen, et al., "HfOx based vertical resistive randomaccess memory for cost-effective 3D cross-point architecture without cell selector," Proc. of 2012 International Electron Devices Meeting, IEEE, vol. 20, no. 7, pp. 1-4,2012.

- [7] M. Y. Song, et al., "Realization of one-diode-type resistives witching memory with Cr=SrTiO3 film," Applied PhysicsExpress, vol. 5, no. 9, 091202, 2012.

- [8] G. H. Kim, et al., "32×32 crossbar array resistive memorycomposed of a stacked Schottky diode and unipolar resistive memory," Advanced Functional Materials, vol. 23, no.11, pp. 1440-1449, 2013.

- [9] J. M. Ngaruiya, et al., "Preparation and characterization oftantalum oxide films produced by reactive DC magnetronsputtering," Physica Status Solidi A, vol. 198, no. 1, pp.99-110, 2003.

- [10] T. Tsuruoka, et al., "Effects of moisture on the switching characteristics of oxide-based, gapless-type atomicswitches," Advanced Functional Materials, vol. 22, no. 1,pp. 70-77, 2012.

- [11] Y. Kobayashi, et al., "Nanoporous structure of sputterdeposited silicon oxide films characterized by positroniumannihilation spectroscopy," Journal of Applied Physics, vol. 91, no. 3, pp. 1704-1706, 2002.

- [12] S. Kwon, et al., "Structurally engineered nanoporousTa2O5-x selector-less memristor for high uniformity andlow power consumption," ACS Applied Materials & Interfaces, vol. 9, no. 39, pp.

pp. 34015-34023, 2017.

[13] L. Shi, et al., "Research progress on solutions to the sneak path issue in memristor crossbar arrays," Nanoscale Advances, vol. 2, no. 5, pp. 1811-1827, 2020

[14] G. Wang, et al., "Three-dimensional networked nanoporous Ta2O5-x memory system for ultrahigh densitystorage," Nano Letters, vol. 15, no. 9, pp. 6009-6014,2015.

Min-Woo Kwon received his B.S. and Ph.D. degrees in electrical and computer engineering from Seoul National University (SNU) in 2012 and 2019, respective -ily From 2019 to 2021, he worked at Sam sung Semiconductor Laboratories, where he contributed to the development of 1x nm DRAM cell transistors and their characterization. From 2021 to 2024, , he worked at Gangneung Wonju National University (GWNU) as an assistant professor in the Department of

Electric Engineering. Since 2024, he has been conducting research in the Department of Electronic Engineering at Seoul National University of Science and Technology, where he is currently a professor.

Jongho Lim entered the Department of Electronic Engineering at Gangneung Wonju National University in 2019, and is currently pursuing his B.S. degree. His main research interests include RRAM (Resistive Random Access memor-y). a type of next-generation memory semiconductor device.

Iyung-Hyun Baek was born in Seoul, Korea, in 1990. He received his B.S de ree in Electrical Engineering from Seoul National University (SNU), Seoul, kor as in 2013, and his Ph.D. in Electrical and Computer Engineering from SNU, seo Korea, in 2020. He worked at Samsung Electronics Co., Ltd.(Hwasung, Korea) as a Staff Engineer from 2020 to 2023. In 2023, he joined Gangneung-Wonju

National University (GWNU, Korea) as an assistant professor in the Department of Electronics and Semiconductor Engineering. His main research interests are non volatile memory technologies and neuromorphic systems

### A Second-order Delta-sigma Modulator for Battery Management System DC Measurement

#### Ji-Ho Park, Jun-Ho Boo, Jae-Geun Lim, Hyoung-Jung Kim, Jae-Hyuk Lee, Seong-Bo Park, Joo-Yeul

#### ABSTRACT

This paper presents a second-order modified feed-forward (FF) delta-sigma modulator for battery management system DC measurement. The proposed ADC employs a modified 3-bit feedback digital-to-analog converter (DAC) with the data weight averaging (DWA) technique to improve the capacitance matching. The modified 3-bit DAC reduces the logic complexity of the DWA by simplifying the switching network of unit capacitors. Additionally, the proposed ADC adopts capacitor swapping technique between the input and reference sampling capacitors to minimize its gain error. To further improve the performance of the proposed ADC, system-level lowfrequency chopping (CHL) and correlated double sampling (CDS) are employed to mitigate offset and flicker noise. The prototype ADC is fabricated in a 180 nm CMOS process, and the core area is 0.53 mm2. It consumes 9.48 µWfrom a 1.8 V supply voltage at an operating clock frequency of 19.2 kHz with an oversampling ratio (OSR) of 256. It achieves a dynamic range (DR) of 102.4 dB, a resolution of 7 µVrms, and an offset of 6.86 µV, resulting in aSchreier figure-of-merit (FoM) of 165.3 dB.

*Index terms:* Analog-to-digital converter (ADC), delta-sigma modulator, data weight averaging (DWA), digital-toanalog converter (DAC), feed-forward (FF

#### I. INTRODUCTION

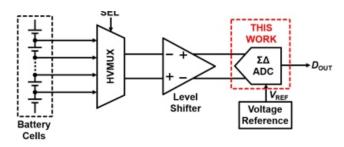

In a battery management system (BMS), a voltage sensing integrated circuit (IC) is an essential block for monitoring the state of charge (SOC), which indicates the remaining power of the battery cells [1-4]. Fig. 1 illustrates the block diagram of the voltage sensing IC for BMS, which consists of a high voltage multiplexer (HVMUX) to select battery cells, a level shifter to scale down the highvoltage of the battery cells, a voltage reference generator, and an analog-to-digital converter (ADC) [1]. Amongthese, the key building block is the ADC which requires

Fig. 1. Block diagram of the voltage sensing IC for BMS.

high-resolution, and delta-sigma ADCs are well suited for the voltage sensing because they can achieve high accuracy through oversampling and noise shaping [5,6]. In the delta-sigma ADCs, an input feed-forward (FF) topology is widely used for high-resolution because iteases the design requirements of the integrators by processing the quantization noise only [7]. This allows forthe reduction of quantization noise and the swing range of the integrators by employing a multi-bit digital-to-analogounverter (DAC), and the DWA is used to correct the mis-match of unit capacitors in the DAC [8]. However, due to signal attenuation within the internal FF path, the comparator accuracy requirements become more challenging, and the load capacitance of the first integrator is affected by the quantizer, reducing power efficiency. Given these constraints, the modified FF topology [9,10], which removes the internal FF path, has emerged. The load capacitance of the first integrator is no longer affected by the quantizer, and simplified passive summing reduces signal attenuation.

In addition to the power efficient topology described above, the proposed architecture employs a modified 3-bit feedback DAC with data weight averaging (DWA). The modified DAC reduces the complexity of the DWAlogic, thereby increasing power and area efficiency. The proposed modulator is fabricated in a 180 nm CMOS process, and achieves a dynamic range (DR) of 102.4 dB and a Schreier figure-of-merit (FoM) of 165.3 dB. The rest of this article is organized as follows: Section III explains the architecture of the proposed delta-sigmamodulator. Section III discusses the details of the circuit implementation. The measurement results of the prototype modulator are presented in Section IV, and this article concludes with Section V.

#### II. PROPOSED ARCHITECTURE

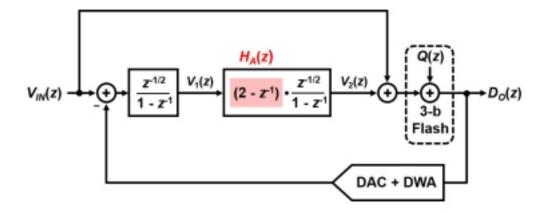

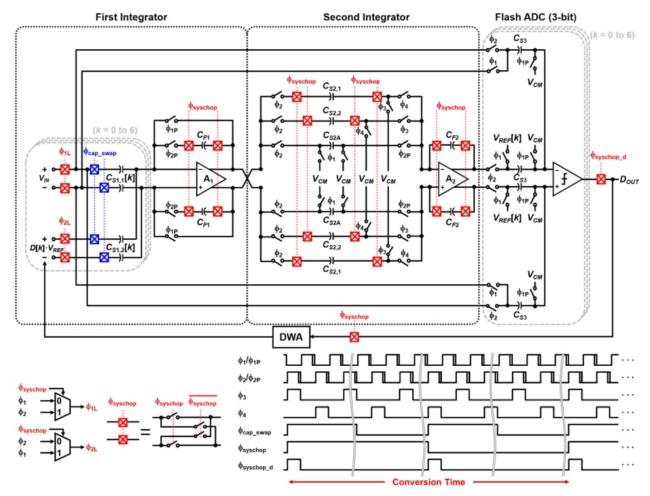

The architecture of the proposed delta-sigma modulator is shown in Fig. 2. The modulator employs the modified FF topology and consists of a first integrator, a second integrator with an analog signal processing block, HA(z), a 3-bit flash quantizer with a passive switched capacitor(SC) adder, and a feedback DAC with DWA. The output of the modulator, DO(z), and the outputs of two integrators, V1(z) and V2(z), are given by

$$D_O(z) = U(z) \cdot STF(z) + Q(z) \cdot NTF(z), \qquad (1)$$

$$V_1(z) = Q(z) \cdot z^{-\frac{1}{2}} \cdot (1 - z^{-1}), \tag{2}$$

$$V_2(z) = Q(z) \cdot z^{-1} \cdot (2 - z^{-1}),$$

(3)

Fig. 2. Architecture of the proposed delta-sigma modulator.

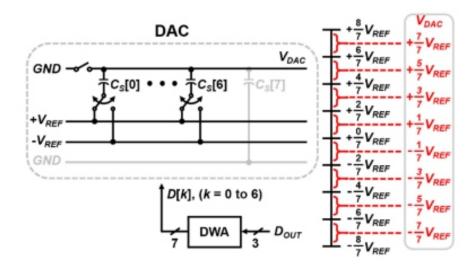

Fig. 3. The modified DAC with DWA and the output levels.

where VIN(z) and Q(z) indicate the input of the modulator and quantization noise, respectively. Thanks to the modified FF topology, integrators handle only quantizationnoise as shown in (2) and (3), which reduces the swingrange of the integrators [9,10]. Also, due to HA(z) in the modified FF architecture, the design requirement of the comparators is relaxed, and power efficiency is increased.

For the feedback DAC, the proposed ADC adopts amodified 3-bit DAC with seven unit capacitors, removingone capacitor connected to ground, as shown in Fig. 3. In the modified DAC, all of the bottom plates of the capacitors switch only between +VREF and -VREF, which simplifies the DWA logic complexity. The DAC output ranges from -7/7VREF to +7/7VREF in steps of 2/7VREF. To reduce the mismatch between unit capacitors, the conventional DWA technique is applied [8].

#### III. CIRCUIT IMPLEMENTATION

#### 1. Proposed Delta-Sigma Modulator

The overall schematic of the proposed delta-sigma modulator and its timing are shown in Fig. 4. The modulator is implemented in a fully differential structure and operates with two non-overlapping clocks,  $\varphi 1$  and  $\varphi 2$ . In the first integrator, DWA is employed to minimize the capacitance mismatch, and its operation is as follows. In the  $\varphi 1$  phase, the flash quantizer determines the 3-bit digital output, and in the  $\varphi 2$  phase, the reference sampling capacitors are shifted according to the output code. Two additional clock signals  $\varphi 3$  and  $\varphi 4$  are employed to implement the transfer function 2-z-1 of the second integrator. Using the thermal noise analysis presented in [11], the sampling capacitance values for both integrators were determined. To reduce the degradation of modulator performance due to thermal noise, the total sampling capac

Fig. 4. The overall schematic of the proposed second-order modified FF delta-sigma modulator and its timing.

tance of the first integrator is set to be 1.5 pF, that of the second integrator to 200 fF, and the input capacitance of the quantizer to 100 fF, since the thermal noise generated in the second integrator and the quantizer is shaped, allowing for smaller capacitor values [11].

A resistive-ladder (R-ladder) has been used on-chipto generate the reference voltage for the flash quantizer. Since static current is produced in the R-ladder, increasing the total resistance reduces power

consumption. However, feedthrough caused by the input stage capacitance between the quantizer's input and the reference voltageleads to distortion in the ADC [12]. To address this, themaximum feedthrough at the midpoint of the R-ladder islimited to 0.1 LSB. The total resistance is determined by the following equation

$$R = \frac{4\phi}{\pi 2^n f_{in} C},\tag{4}$$

where  $\varphi$  is the feedthrough in LSB and n is the resolution of the quantizer and C is the total capacitance from the Rladder, and fin is the input frequency of the quantizer [12]. As a result, the total resistance must be set below 1.18M $\Omega$ . Considering feedthrough and static current, a total resistance of 0.93 M $\Omega$  was chosen. This R-ladder occupies an area of 0.07 mm2.

Correlated double sampling (CDS) is employed in the first integrator to mitigate offset and flicker noise[13]. Furthermore, A system-level low-frequency chopping (CHL) technique suppresses the residual offset ofthe modulator by periodically inverting the polarity ofthe input and output [14]. Therefore, chopped switchesare employed at the input and output paths. In this design, the chopped switch control clock, φsyschop, is used to enable one CHL transition in one conversion cycle. To match the polarity of the integration path between before and after the CHL transition, chopped switches employed for the feedback capacitors. Additionally, the chopped switches are also employed in the sampling capacitors of the second integrator, except for the additional sampling capacitor, CS2A, which is reset in the φ1 phase. During the first reference sampling after the CHL transition, since the modulator output which provides feedback to the DAC has the same polarity as the previous tate, a φsyschop\_d clock signal is used to invert the output polarity of the feedback path to match the polarity of the input and feedback DAC [15]. This process modulates the systematic offset and removes it after passing through the decimation filter.

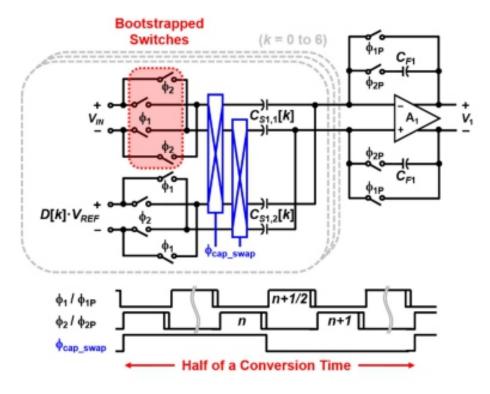

#### 2. Loop Filter

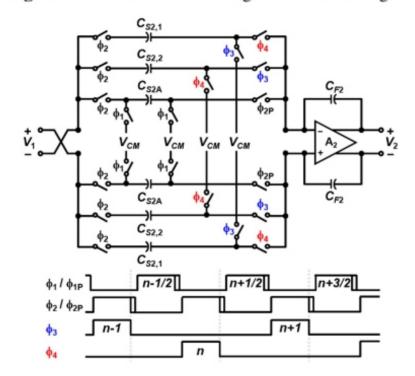

The schematic of the first integrator and its timing are shown in Fig. 5. Bootstrapped switches are employed to enhance input sampling linearity [16]. To reduceADC gain error caused by the capacitance mismatch between the input sampling capacitor CS1,1[k] and the reference sampling capacitor CS1,2[k], a capacitor swappingtechnique is employed to average out the capacitancemismatch as follows: During one conversion cycle, theCS1,1[k] and CS1,2[k] arrays are swapped twice to ensure that the averaged capacitance is used for both input andreference sampling. The schematic of the second integrator with the transfer function, 2-z-1, and its timing are shown in Fig. 6. For the second

integrator, three sampling capacitors are employed: two sampling capacitors CS2,1,CS2,2, and an additional capacitor CS2A. During the following  $\varphi 3$  phase, CS2,2 and CS2A are connected to integrate theoutput of the first integratorV1[n-1] without delay. At this time, the remainingCS2,1 samples the output of the first integrator. Then, during the subsequent  $\varphi 1$  phase, CS2A is re

Fig. 5. Schematic of the first integrator and its timing.

Fig. 6. Schematic of the second integrator and its timing.

set. In the following  $\varphi 4$  phase, similar to the  $\varphi 3$  phase, the previously sampled CS2,1 and CS2A are connected for integration. Finally, the output of the second integrator V2[n]becomes 2  $\cdot$ V1[n]-V1[n-1], and this sequence of operations implements the transfer function 2-z-1.

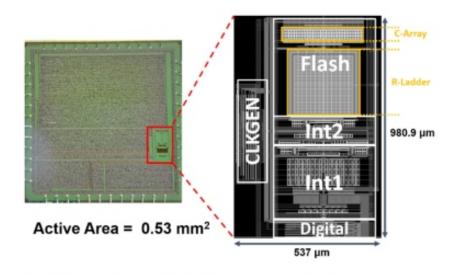

## IV. MEASUREMENT RESULTS

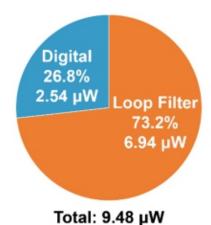

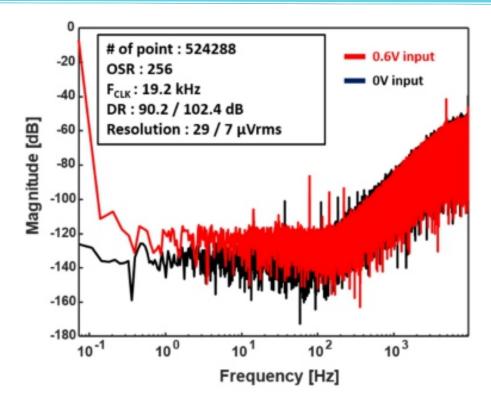

The prototype delta-sigma modulator is implemented in a 180 nm CMOS process. Fig. 7 shows the die micrographof the proposed modulator. The core area is 0.53 mm2. Fig. 8 shows the power breakdown of the proposed modulator. From a 1.8 V supply, the modulator consumes 9.48  $\mu$ W at 19.2 kHz sampling frequency. Fig. 9 shows the measured output spectrum of the proposed modulator with a 0.6 VDC input and input shorted, respectively. The measured DR is 102.4 dB and Fig. 10 shows the measured offset

Fig. 7. Die micrograph of the proposed modulator.

Fig. 8. Power breakdown of the proposed modulator.

Fig. 9. Measured output spectrum of the proposed modulator.

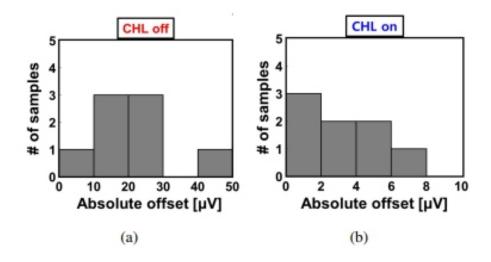

Fig. 10. Measured offset of the proposed modulator with (a) chopped off, and (b) chopped on.

with and without CHL, and for this measurement, a sinc3 filter is implemented off-chip for decimation in MATLAB. The maximum offset from eight samples without CHL is 50  $\mu$ V, and it drops below 6.86  $\mu$ V with CHL. The measured performance of the proposed modulator is summarized and compared in Table 1.

|                                    | This work | [17]   | [18]   | [19]    | [20]   |  |

|------------------------------------|-----------|--------|--------|---------|--------|--|

| Architecture                       | DT DSM    | CT DSM | CT DSM | DT IDSM | DT DSM |  |

| Process (nm)                       | 180       | 65     | 180    | 180     | 110    |  |

| F <sub>CLS</sub> (kHz)             | 19.2      | 0.512  | 64     | 5000    | 512    |  |

| OSR                                | 256       | 256    | 128    | 250     | 128    |  |

| BW (Hz)                            | 18.75     | 1      | 250    | 10000   | 2000   |  |

| Supply (V)                         | 1.8       | 1.2    | 1.8    | 1.8     | 1.5    |  |

| Power (µW)                         | 9.48      | 15     | 2.16   | 83      | 62.43  |  |

| DR (dB)                            | 102.4     | 105    | 81.4   | 89.1    | 96.3   |  |

| Resolution<br>(µV <sub>rms</sub> ) | 7         | 4      | -      | 19      | -      |  |

| Offset (µV)                        | 6.86      | -      | -      | -       | -      |  |

| Area (mm <sup>2</sup> )            | 0.523     | 9.07   | 0.29   | 0.35    | 0.165  |  |

| *FoM <sub>s</sub>                  | 165       | 153    | 162    | 162     | 171    |  |

Table 1. Performance summary and comparison table.

## V. CONCLUSION

This paper presents a second-order modified FF deltasigma modulator for BMS DC measurement. The proposed modulator employs the modified 3-bit feedback DAC to reduce the complexity of the DWA logic, and a capacitor swapping technique is adopted to minimize the gain error from sampling capacitance mismatch. Additionally, the CDS and CHL techniques are applied to minimize offset and flicker noise. The prototype modulator, fabricated in a 180 nm CMOS process, achieved a DR of102.4 dB, a resolution of  $7\,\mu\text{Vrms}$ , and an offset of  $6.86\,\mu\text{V}$  while consuming  $9.48\,\mu\text{W}$ .

## **ACKNOWLEDGMENTS**

This work was supported by Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (P0017011, HRD programfor Industrial Innovation) and was supported by the MSIT (Ministry of Science and ICT), Korea, under the ITRC (Information Technology Research Center) support program (IITP-2024-RS-2023-00260091) supervised by the IITP (Institute for Information & Communications Technology Planning & Evaluation). The EDA tool was supported by the IC Design Education Center (IDEC), Korea and the chip fabrication was supported by the

$<sup>*</sup>FoM_s = DR + 10 \cdot log_{10}(BW/Power)$

LX Semicon Co., Ltd.

#### REFERENCES

- [1] J.-K. Lee, et al., "ASIL-D compliant battery monitoring IC with high measurement accuracy and robust communication," Proc. of 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, pp.322-324, 2023.

- [2] K. Kadirvel, J. Carpenter, P. Huynh, J. M. Ross, R. Shoemaker, and B. Lum-Shue-Chan, "A stackable, 6-cell, LiIon, battery management IC for electric vehicles with 13, 12-bit  $\Sigma\Delta$  ADCs, cell balancing, and direct-connect current-mode communications," IEEE Journal of SolidState Circuits, vol. 49, no. 4, pp. 928-934, April 2014.

- [3] Z.-Y. Hou, P.-Y. Lou, and C.-C. Wang, "State of charge, state of health, and state of function monitoring for EV BMS," Proc. of 2017 IEEE International Conference on Consumer Electronics (ICCE), Las Vegas, NV, USA, pp. 310-311, 2017.

- [4] J.-H. Boo, et al., "A single-trim switched capacitor CMOS bandgap reference with a  $3\sigma$  inaccuracy of +0.02%, -0.12% for battery-monitoring applications," IEEE Journal of Solid-State Circuits, vol. 56, no. 4, pp. 1197-1206, April 2021.

- [5] Linear Technology, LTC2947-65 Data sheet, Accessed: Oct. 2023. [Online]. Available: https://www.analog.com/media/en/technicaldocumentation/data-sheets/LTC2947-65.pdf.

- [6] Texas Instruments. BQ76905 2-Series to 5-Series HighAccuracy Battery Monitor and Protector for Li-Ion,Li-Polymer, LiFePO4(LFP), and LTO Battery Packs Data sheet, Accessed: Nov. 2023. [Online]. Available: https://www.ti.com/lit/pdf/SLUSE97.

- [7] J. Silva, U. Moon, J. Steensguqrd, and G. C. Temes, "Wide band low distortion delta-sigma ADC topology," IEE Electron. Lett., vol. 37, no.12, pp. 737–738, Jun. 2001.

- [8] R. T. Braird and T. S. Fiez, "Linearity enhancement of multi-bit  $\Sigma\Delta$  A/D and D/A converters using data weighted averaging," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 42, no. 12, pp. 753–762, Dec. 1995.

- [9] K. Cho, Y. Kwak, H. Kim, and G. Ahn, "A 101 dB dynamic range, 2kHz bandwidth delta-sigma modulator with a modified feedforward architecture," IEICE Electron. Exp., vol. 15, no. 21, Art. no. 20180848, 2018.

- [10] B.-H. Yu, et.al., "A 97.7-dB DR 12.3-µW 1-kHz Bandwidth 2nd order delta-sigma modulator with a fully differential class-AB Op-Amp using floating class-AB control," J. Semicoductor Technology and Science (JSTS), vol. 23, no. 5, pp. 265-272, Oct. 2023.

- [11] R. Schreier, J. Silva, J. Steensgaard, and G. C. Temes, "Design-oriented estimation of thermal noise in switchedcapacitor circuits," IEEE Transactions on Circuits and Systems I: Regular Papers,

- vol. 52, no. 11, pp. 2358-2368, Nov. 2005.

- [12] A. G. W. Venes and R. J. van-de-Plassche, "An 80-MHz, 80-mW, 8-b CMOS folding A/D converter with distributedtrack-and-hold preprocessing," IEEE Journal of SolidState Circuits, vol. 31, no. 12, pp. 1846-1853, Dec. 1996.

- [13] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," Proceedings of IEEE, vol. 84, no. 11, pp. 1584-1614, Nov.1996.

- [14] M. A. P. Pertijs, K. A. A. Makinwa, and J. H. Huijsing, "A CMOS smart temperature sensor with a  $3\sigma$  inaccuracyof±0.1°C from -55°C to 125°C," IEEE Journal of SolidState Circuits, vol. 40, no. 12, pp. 2805-2815, Dec. 2005

- .[15] Z. Tang, R. Zamparette, Y. Furuta, T. Nezuka, and K. A. A.Makinwa, "A versatile  $\pm 25$ -A shunt-based current sensorwith  $\pm 0.25\%$  gain error from -40°C to 85°C," IEEE Journal of Solid-State Circuits, vol. 57, no. 12, pp. 3716-3725,Dec. 2022.

- [16] M. Dessouky and A. Kaiser, "Very low-voltage digital audio  $\Sigma\Delta$  modulator with 88-dB dynamic range using local switch bootstrapping," IEEE Journal of Solid-State Circuits, vol. 36, no. 3, pp. 349-355, March 2001.

- [17] J. Aymerich, et al., "A 15-µW 105-dB 1.8-Vpp Potentiostatic delta-sigma modulator for wearable electrochemicaltransducers in 65-nm CMOS technology," IEEE Access,vol. 8, pp. 62127-62136, 2020.

- [18] J. Kim, Q. Duan, J. Choi, C. Song, and J. Roh, "A2.16-µW low-power continuous-time deltasigma modulator with improved-linearity Gm for wearable ECG application," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 69, no. 11, pp. 4223-4227, Nov. 2022.

- [19] J. Liang and D. A. Johns, "A frequency-scalable 15-bit incremental ADC for low power sensor applications," Proc. of 2010 IEEE International Symposium on Circuits and Systems, Paris, France, pp. 2418-2421, 2010.

- [20] J. Han, K. Cho, H. Kim, J. Boo, J. Kim, and G. Ahn, "A 96dB dynamic range 2kHz bandwidth 2nd order deltasigma modulator using modified feed-forward architecturewith delayed feedback," IEEE Trans. Circuits Syst. II, Exp.Briefs, vol. 68, no. 5, pp. 1645-1649, May 2021.

Ji-Ho Park received the B.S. degree in electronic engineering from Sogang U -niversity, Seoul, Korea, in 2023, where he is currently pursuing the M.S. degree. Mr.Park is a recipient of a scholarship sponsored by Samsung electron -ic. His current research interests include high-resolution data converters and sensor interfaces.

Jun-Ho Boo received the B.S. and Ph.D. degrees in electronic engineering from Sogang University, Seoul, Korea, in 2017 and 2023,, respectively. From 2023 to 2025, he was a Staff Engineer at Memory Division, Samsung Electronics, Hwaseong, Korea. His current research interests include analogand mixed-signal circuits, data converters, and sensor interfaces.

Jae-Geun Lim received the B.S. degree in electronic engineering from Sogang University, Seoul, Korea, in 2019, where he is currently pursuing the Ph.D. de -gree. Mr. Lim is a recipient of a scholarship sponsored by Samsung electronics. His current research interests include low-power and high-speed analog- to -digital converter.

Hyoung-Jung Kim received the B.S. degree in electronic engineering from Sog -ang University, Seoul, Korea, in 2020, where he is currently pursuing the Phd degree. Mr. Kim is a recipient of a scholarship sponsored by Samsung electron ics. His current interests are in the design of low-power and high-speed analog -to - digital converter.

Jae-Hyuk Lee received the B.S. degree in electronic engineering from Sogan -g University, Seoul, Korea, in 2020, where he is currently pursuing the phd degree. Mr. Lee is a recipient of a scholarship sponsored by Samsung electro -nics. His current interests are in the design of high speed, high-resolution CMOS data converters, and very high-speed mixed-mode integrated

systems.

Seong-Bo Park received the B.S. degree in electronic engineering from Soga -ag University, Seoul, Korea, in 2022, where he is currently pursuing the Ph.D. degree. His current research interests include data converters, and sensor interfaces.

Joo-Yeul Yang received the B.S. degree in electronic engineering from Sog -ang University, Seoul, Korea, in 2023, where he is currently pursuing the M.S. degree. Mr. Yang is a recipient of a scholarship sponsored by Samsu -ng electronics. His current research interests include data converters and mixed-signal circuit design.

Gil-Cho Ahn received the B.S. and M.S. degrees in electronic engineering from Sogang University, Seoul, Korea,in 1994 and 1996, respectively, and the Ph.D. degree in electrical engineering from Oregon State University, Corvallis, in 2005. From 1996 to 2001, he was a Design Engineer at Samsu -ng Electronics, Kiheung, Korea, working on mixed analog digital integrat

ed circuits. From 2005 to 2008, he was with Broadcom Corporation, Irvine, CA, working on AFE for digital TV. Currently, he is a Professor in the Department of Electronic Engineering, Sogang University. His research interests include high-speed, high-resolution data converters and low-voltage, low-power mixed-signal circuits design.

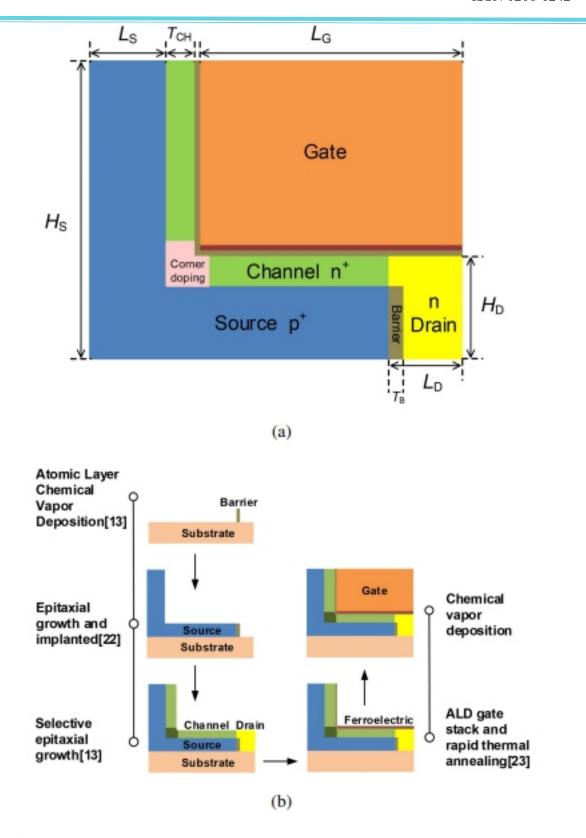

# Design Optimization of L-Shaped Gate Negative Capacitance Si/Ge Heterojunction TFET With Channel Doping

Xinfeng Zheng, Weifeng Lü, Yubin Wang, Shuaiwei Zhao, and Honglei Huo

## ABSTRACT

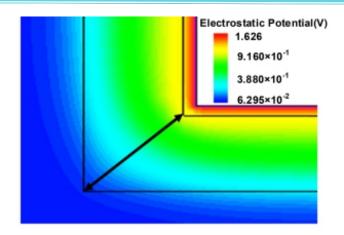

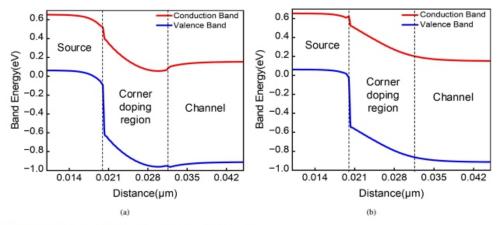

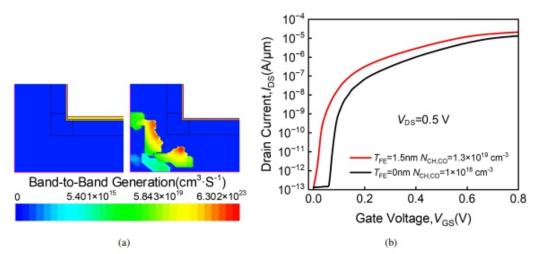

In this paper, to improve the performance of L-shaped gate heterojunction tunneling field-effect transistor (LG-HJ-TFET), an L-shaped gate negative capacitance Si/Ge heterojunction TFET with channel doping (NCHJCD-LTFET) was proposed, whose electrical characteristics were investigated through technology computer-aideddesign simulations in Sentaurus. The NCHJ-CD-LTFET has doping (n+-doping for an n-type TFET) in the cornerregion of the channel, which plays an important role in modulating the energy bands that reduce the bandgap between the source and channel in the doping area. Thus, compared with the LG-HJ-TFET, the band-to-band tunneling of NCHJ-CD-LTFET occurs at a lower gate voltage (VGS), and the threshold voltage (VTH) is significantly reducedfrom 0.221 to 0.181 V. In addition, a ferroelectric layer was deposited above the horizontal gate dielectric to furtherimprove the electrical characteristics owing to the negative-capacitance effects. With comprehensive adjustment thedoping concentration of the channel corner region (NCH,CO) and the thickness of the ferroelectric layer (TFE), theNCHJ-CD-LTFET had a low VTH of 0.145 V, a high on-state current (ION) of 27.5  $\mu$ A/ $\mu$ m, a high switching currentratio (ION/IOFF) of 2.1×108 and a steep average subthreshold slope (SSAVE) of 24.92 mV/decade.

*Index terms:* Band-to-band tunneling, L-shaped gate TFET, negative capacitance, channel doping, energy band modulation

## I. INTRODUCTION

With the development of integrated circuits, the number of transistors on a chip and the operating frequency are increasing. Although these improve the chip performance, they also increase the power consumption [1]. Because complementary metal-oxide-semiconductor devicesrely on thermal injection as the carrier emission mechanism, their subthreshold slope (SS) cannot be lower than 60 mV/decade at room temperature, owing to Boltzmann's tyranny [2], resulting in a transistor that does not satisfy both the high-performance and low-power consumption requirements. Fortunately, tunneling field-effect traistors (TFETs) that utilize quantum-mechanical bandto-band tunneling (BTBT) can overcome Boltzmann's tyranny and obtain sub-60 mV/decade SSs [3-9]. However, conventional TFETs have drawbacks, such as their low on-state currents (ION) [10,11]. In many proposed TFETs structures, such as L-TFETs [12,13], U-TFETs [14], and Z-TFETs [15], ION is increased by increasing the BTBT area. In particular, the performance of L-shaped channel TFETs has

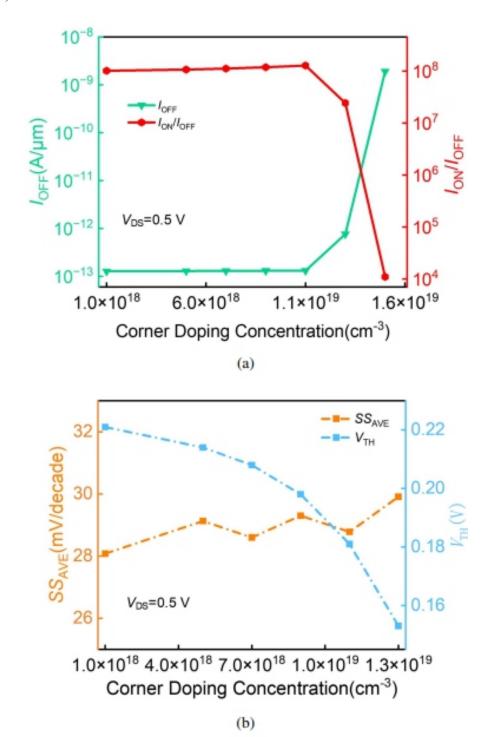

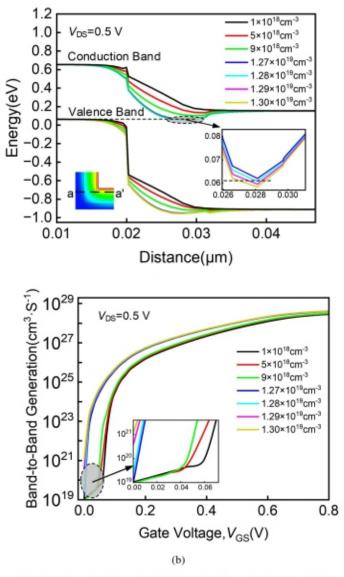

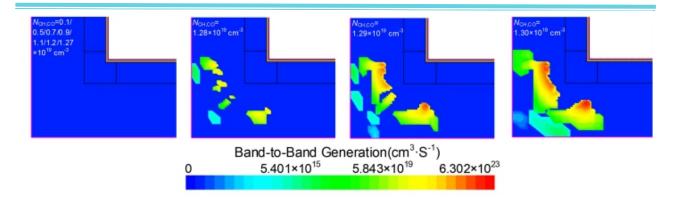

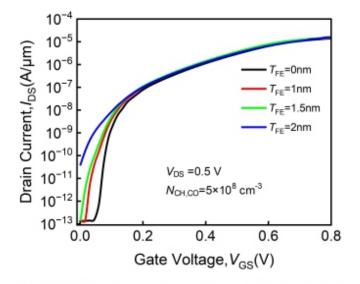

been improved via doping or the addition of ferroelectric layers [16-19]. Doping engineering can achieve abrupt switching by mitigating the BTBT at the corner edge of the source region in a negative capacitance TFET (NCTFET) [18]. Recently, an L-shaped gate InGaAs/GaAsSb heterojunction TFET was presentedthat extends the source to increase the BTBT area between source and channel for increasing ION [20]. However, few studies have focused on capacitance Si/Ge heterojunction tunneling field-effect transistor with channel doping (NCHJ-CD-LTFET) wasdeveloped and investigated via technology computeraided design (TCAD) simulations with calibrated modelparameters [21]. Compared with the LG-HJ-TFET, theNCHJ-CD-LTFET has a far lower threshold voltage (VTH). The energy bands of the corner doping region are modulated via channel doping, which reduces the tunneling barrier between the source and the channel and theferroelectric layer can amplify the internal gate voltageto increase the electric potential of the channel surface. Meanwhile, the negative-capacitance effects can suppressBTBT at VGS = 0 V and reduce the off-state current (IOFF). The doping concentration of the channel corner region(NCH,CO) and the ferroelectric-layer thickness (TFE) canbe adjusted to optimize the electrical performance of the device, lowing power consumption and improving drive capability.

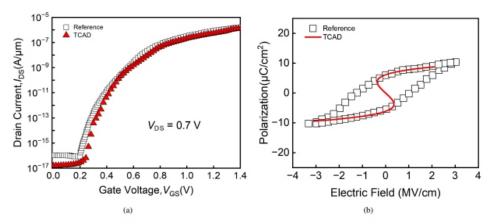

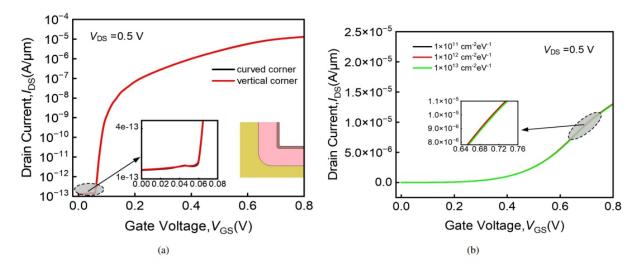

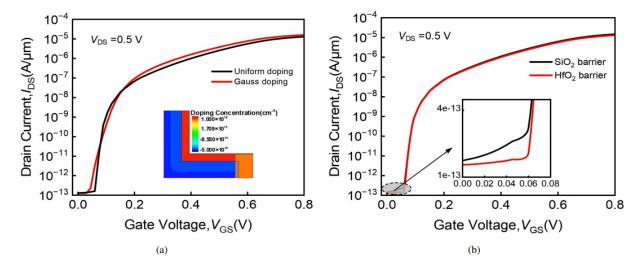

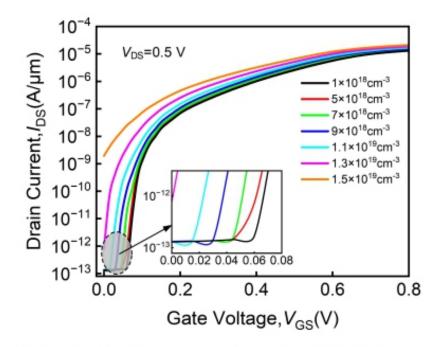

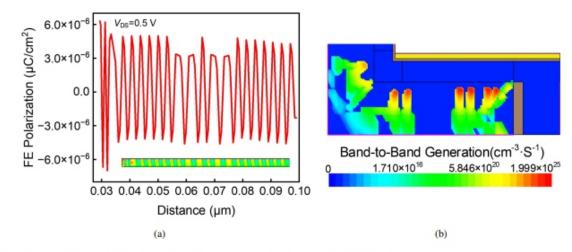

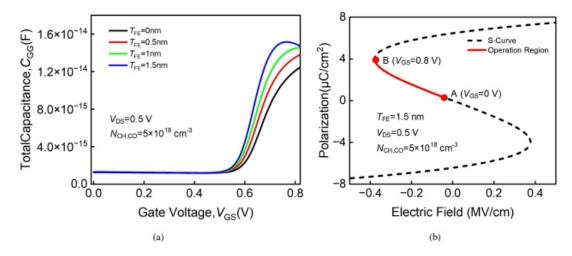

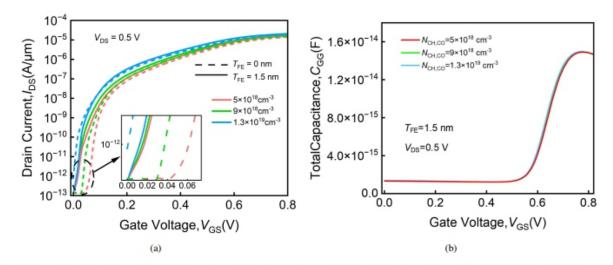

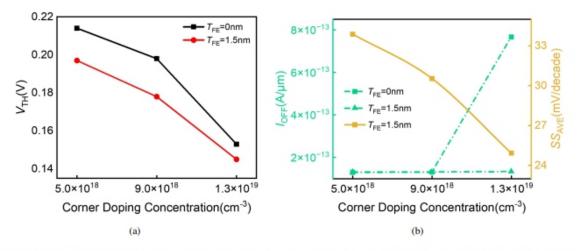

## II. STRUCTURE AND MECHANISM OF THE NCHJ-CD-LTFET